Data Sheet

#### July 7, 2004

# Video Front End

intercil

The EL4501 is a highly-integrated Video Front End (VFE) incorporating all of the key signal conditioning

functions for analog video signals. It provides a flexible frontend interface for analog or analog/digital video sub-systems. The VFE contains a high bandwidth DC-restore, an advanced sync separator and a data slicer with an adjustable threshold, configurable output and power-down mode.

The VFE performs restoration of the DC level (blanking level) of a video signal and the recovery of all signal timing necessary for synchronization and control. Additionally, data embedded in the active video or VBI regions of the video signal may be extracted using the flexible data slicer incorporated into the VFE. The advanced sync separator exhibits excellent noise immunity by incorporating a digital brick wall filter and signal qualification algorithm. The DC-restored video amplifier is unity gain stable with an unloaded -3dB bandwidth of 100MHz. The input common mode voltage range extends from the negative rail to within 1.5V of the positive rail. When driving a 75 $\Omega$  double terminated coaxial cable, the amplifier can drive to within 150mV of either rail. With 200V/µs slew rate, the amplifier is well suited for composite and component video applications.

The VFE operates from a single 5V supply from -40°C to +85°C and is available in a reduced footprint 24-pin QSOP package.

# Ordering Information

| PART<br>NUMBER               | PACKAGE                  | TAPE & REEL | PKG. DWG. # |

|------------------------------|--------------------------|-------------|-------------|

| EL4501IU                     | 24-Pin QSOP              | -           | MDP0040     |

| EL4501IU-T7                  | 24-Pin QSOP              | 7"          | MDP0040     |

| EL4501IU-T13                 | 24-Pin QSOP              | 13"         | MDP0040     |

| EL4501IUZ<br>(See Note)      | 24-Pin QSOP<br>(Pb-free) | -           | MDP0040     |

| EL4501IUZ-T7<br>(See Note)   | 24-Pin QSOP<br>(Pb-free) | 7"          | MDP0040     |

| EL4501IUZ-<br>T13 (See Note) | 24-Pin QSOP<br>(Pb-free) | 13"         | MDP0040     |

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matter tin plate termination finish, which is compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J Std-020B.

# Features

- · DC-restore and sync separator

- · Wideband (100MHz) DC-restore

- Advanced sync separator

- Programmable data slicer

- Single 5V operation

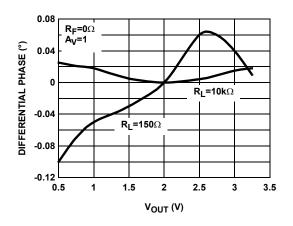

- Diff gain/phase =  $0.05\%/0.03^{\circ}$ , R<sub>L</sub>= $10k\Omega$ , A<sub>V</sub>=1

- Low power (<75mW)

- · Pb-free available

# Applications

- · Video capture & editing

- Video projectors

- Set top boxes

- Security video

- · Embedded data recovery

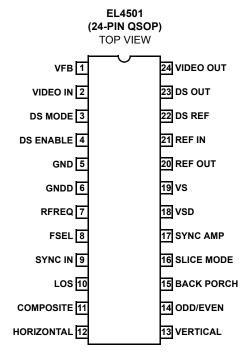

# Pinout

# Absolute Maximum Ratings (T<sub>A</sub> = 25°C)

| Supply Voltage (V <sub>S</sub> to GND) | +6V                              |

|----------------------------------------|----------------------------------|

| Pin Voltage                            | .GND -0.3V, V <sub>S</sub> +0.3V |

| Storage Temperature Range              | 65°C to +150°C                   |

| Ambient Operating Temperature          | 40°C to +85°C                    |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

| <b>Electrical Specifications</b> | V <sub>S</sub> = V <sub>SD</sub> = 5V, GND | = 0V, T <sub>A</sub> = 25°C, Input Video = | = 1V <sub>P-P</sub> , R <sub>FREQ</sub> = 130kΩ |

|----------------------------------|--------------------------------------------|--------------------------------------------|-------------------------------------------------|

|----------------------------------|--------------------------------------------|--------------------------------------------|-------------------------------------------------|

| PARAMETER         | DESCRIPTION                                   | CONDITIONS                                                                  | MIN  | ТҮР   | MAX  | UNIT  |

|-------------------|-----------------------------------------------|-----------------------------------------------------------------------------|------|-------|------|-------|

| I <sub>SA</sub>   | Input Supply Current                          | No load                                                                     | 7.5  | 10.5  | 13.5 | mA    |

| I <sub>SD</sub>   | Digital Supply Current                        | No load, V <sub>IN</sub> = 0V                                               | 1.9  | 2.3   | 4    | mA    |

| V <sub>S</sub>    | Input Supply Voltage Range                    |                                                                             | 4.5  |       | 5.5  | V     |

| V <sub>SD</sub>   | Digital Input Supply Voltage Range            |                                                                             | 4.5  |       | 5.5  | V     |

| VIDEO AMPLII      | FIER SECTION                                  | 1                                                                           |      |       |      |       |

| V <sub>OP</sub>   | Positive Output Voltage Swing (VIDEO OUT)     | $R_L$ = 150 $\Omega$ to V <sub>S</sub> / 2                                  | 4.65 | 4.70  |      | V     |

|                   | (Note 1)                                      | $R_L = 150\Omega$ to GND                                                    | 4.20 | 4.60  |      | V     |

|                   |                                               | $R_L = 1k\Omega$ to $V_S / 2$                                               | 4.85 | 4.90  |      | V     |

| V <sub>ON</sub>   | Negative Output Voltage Swing (VIDEO OUT)     | $R_L$ = 150 $\Omega$ to V <sub>S</sub> / 2                                  |      | 0.15  | 0.30 | V     |

|                   | (Note 1)                                      | $R_L = 150\Omega$ to GND                                                    |      | 0.06  | 0.25 | V     |

|                   |                                               | $R_L = 1k\Omega$ to $V_S / 2$                                               |      | 0.05  | 0.20 | V     |

| +IOUT             | Positive Output Current (VIDEO OUT)           | $R_L$ = 10 $\Omega$ to V <sub>S</sub> / 2                                   | 60   | 70    |      | mA    |

| -Iout             | Negative Output Current (VIDEO OUT)           | $R_L$ = 10 $\Omega$ to V <sub>S</sub> / 2                                   | -50  | -60   |      | mA    |

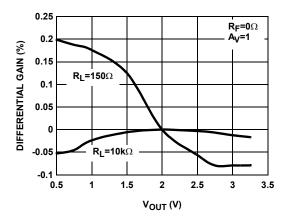

| dG                | Differential Gain Error (VIDEO OUT) (Note 2)  | $A_V = 1, R_L = 10 k\Omega, R_F = 0\Omega$                                  |      | 0.05  |      | %     |

| dP                | Differential Phase Error (VIDEO OUT) (Note 2) | A <sub>V</sub> = 1, R <sub>L</sub> = 10kΩ, R <sub>F</sub> = 0Ω              |      | 0.03  |      | 0     |

| BW                | Bandwidth                                     | -3dB, G = 1, $R_L$ = 10k $\Omega$ to GND, $R_F$ = 0                         |      | 100   |      | MHz   |

|                   |                                               | -3dB, G = 1, $R_L$ = 150 $\Omega$ to GND, $R_F$ = 0                         |      | 60    |      | MHz   |

| BW1               | Bandwidth                                     | $\pm 0.1$ dB, G = 2, R <sub>L</sub> = 150 $\Omega$ to GND                   |      | 8     |      | MHz   |

| SR                | Slew Rate                                     | 25% to 75%, 3.5V <sub>P-P</sub> , R <sub>L</sub> = 150Ω, R <sub>F</sub> = 0 | 80   | 96    |      | V/µs  |

| V <sub>RL</sub>   | Ref Level Range                               |                                                                             |      | 0/3.5 |      | V     |

| t <sub>S</sub>    | Settling Time                                 | to 0.1%, V <sub>IN</sub> = 0V to 3V                                         |      | 35    |      | ns    |

| R <sub>IN</sub>   | Input Resistance (VIDEO IN)                   |                                                                             |      | 115   |      | kΩ    |

| C <sub>IN</sub>   | Input Capacitance (VIDEO IN)                  |                                                                             |      | 1.5   |      | pF    |

| A <sub>VOL</sub>  | Open Loop Voltage Gain                        | R <sub>L</sub> = no load, V <sub>OUT</sub> = 0.5V to 3V                     |      | 65    |      | dB    |

|                   |                                               | $R_L$ = 150 $\Omega$ to GND, $V_{OUT}$ = 0.5V to 3V                         |      | 50    |      | dB    |

| DC-RESTORE        | SECTION                                       |                                                                             |      |       |      |       |

| CMIR              | Common Mode Input Range (REF IN)              |                                                                             |      | 0/3.5 |      | V     |

| V <sub>OS</sub>   | Input Offset Voltage                          | DC restored                                                                 |      | ±20   |      | mV    |

| TCV <sub>OS</sub> | Input Offset Voltage Temperature Coefficient  |                                                                             |      | 10    |      | µV/°C |

| IB                | Input Bias Current (REF IN)                   | V <sub>CM</sub> = 0V to 3.5V                                                | -10  | 0.001 | 10   | μA    |

| V <sub>REF</sub>  | Reference Output Voltage (REF OUT)            | I <sub>OUT</sub> = +2mA to -0.5mA                                           | 1.15 | 1.3   | 1.4  | V     |

| <b>Electrical Specifications</b> | $V_S = V_{SD} = 5V$ , GND = 0V, $T_A = 25^{\circ}C$ , Input Video = $1V_{P-P}$ , $R_{FREQ} = 130k\Omega$ (Continued) |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------|

|----------------------------------|----------------------------------------------------------------------------------------------------------------------|

| PARAMETER           | DESCRIPTION                                 | CONDITIONS                                      |      | TYP   | MAX  | UNIT             |

|---------------------|---------------------------------------------|-------------------------------------------------|------|-------|------|------------------|

| I <sub>RMAX</sub>   | Available Restore Current (VFB)             |                                                 |      | 18.5  |      | μA               |

| DATA SLICER         | SECTION                                     |                                                 |      |       |      |                  |

| IIH                 | Input High Current (DS MODE & DS ENABLE)    | V <sub>IH</sub> = 5V                            |      | 6     | 10   | μA               |

| IIL                 | Input Low Current (DS MODE & DS ENABLE)     | V <sub>IL</sub> = 0V                            |      | 200   | 350  | nA               |

| V <sub>IH</sub>     | Input High Voltage (DS MODE & DS<br>ENABLE) |                                                 | 4.5  |       |      | V                |

| VIL                 | Input Low Voltage (DS MODE & DS ENABLE)     |                                                 |      |       | 0.5  | V                |

| V <sub>OH</sub>     | Output High Voltage (DS OUT)                | I <sub>OUT</sub> = -1mA                         | 4.75 | 4.9   |      | V                |

| V <sub>OL</sub>     | Output Low Voltage (DS OUT)                 | I <sub>OUT</sub> = +1mA                         |      | 0.1   | 0.25 | V                |

| IOUT                | Short Circuit Current (DS OUT)              | $R_L = 10\Omega$ to 2.5V                        | 8    | 11    |      | mA               |

| IB                  | Input Bias Current (DS REF)                 | DS REF = 0V to 5V                               | -10  | 0.001 | 10   | μA               |

| V <sub>OS</sub>     | Input Offset Voltage                        |                                                 | -20  |       | +20  | mV               |

| V <sub>HYS</sub>    | Hysteresis                                  |                                                 |      | ±5    |      | mV               |

| t <sub>PD</sub>     | Propagation Delay                           | 50% to 50%                                      |      | 18    |      | ns               |

| t <sub>R/F</sub>    | Rise/Fall Time                              | 10% to 90%, $R_L$ = 150k $\Omega$ , $C_L$ = 5pF |      | 1.2   |      | ns               |

| SYNC SEPAR          | ATOR SECTION                                | 1                                               |      | +     |      | ı                |

| IIH                 | Input High Current (FSEL & SYNC MODE)       | V <sub>IH</sub> = 5V                            | -1   |       | 1    | μA               |

| IIL                 | Input Low Current (FSEL & SYNC MODE)        | V <sub>IL</sub> = 0V                            | -1   |       | 1    | μA               |

| V <sub>IH</sub>     | Input High Voltage (FSEL & SYNC MODE)       |                                                 | 4.5  |       |      | V                |

| V <sub>IL</sub>     | Input Low Voltage (FSEL & SYNC MODE)        |                                                 |      |       | 0.5  | V                |

| V <sub>OH</sub>     | Output High Voltage                         | I <sub>OH</sub> = -1.6mA                        | 4.6  |       |      | V                |

| V <sub>OL</sub>     | Output Low Voltage                          | I <sub>OL</sub> = +1.6mA                        |      |       | 0.4  | V                |

| V <sub>THRSHA</sub> | Adaptive Slice Level                        | SYNC MODE = 0V                                  | 40   | 50    | 60   | %                |

| V <sub>THRSHF</sub> | Fixed Slice Threshold                       | SLICE MODE = $V_S$                              | 80   | 100   | 120  | mV               |

| V <sub>SI</sub>     | SYNC IN Reference Voltage                   |                                                 |      | 1.8   |      | V                |

| R <sub>INSI</sub>   | SYNC IN Input Impedance                     |                                                 |      | 115   |      | kΩ               |

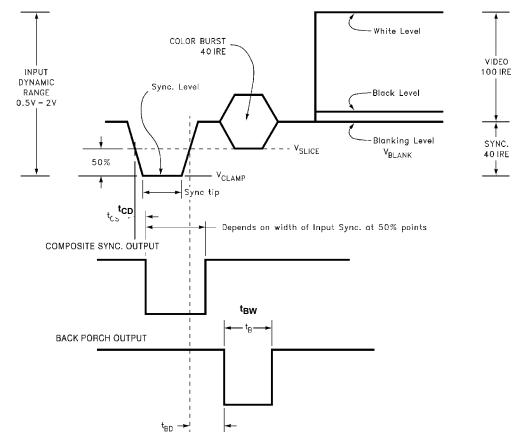

| V <sub>RANGE</sub>  | Input Dynamic Range                         |                                                 | 0.5  |       | 2.0  | V <sub>P-P</sub> |

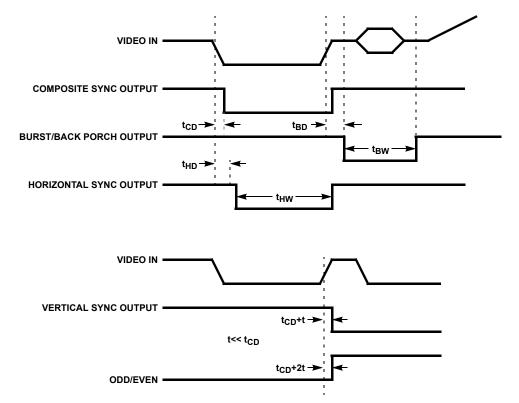

| t <sub>CD</sub>     | COMPOSITE Delay                             | FSEL = 0, from 50% of sync leading edge         | 25   | 35    | 45   | ns               |

| t <sub>CDF</sub>    | COMPOSITE Delay                             | FSEL = 1, from 50% of sync leading edge         | 150  | 225   | 280  | ns               |

| t <sub>BD</sub>     | BACK PORCH Delay                            | FSEL = 0, from 50% of trailing sync edge        | 125  | 170   | 225  | ns               |

| t <sub>BDF</sub>    | BACK PORCH Delay                            | FSEL = 1, from 50% of trailing sync edge        | 250  | 420   | 550  | ns               |

| t <sub>HD</sub>     | HORIZONTAL Delay                            | FSEL = 0/1, from 50% of sync leading edge       | 365  | 470   | 585  | ns               |

| t <sub>BW</sub>     | BACK PORCH Width                            | FSEL = 0/1                                      | 2.8  | 3.2   | 4.1  | μs               |

| t <sub>HW</sub>     | HORIZONTAL Width                            | FSEL = 0                                        | 1.1  | 1.3   | 1.5  | μs               |

| t <sub>HWF</sub>    | HORIZONTAL Width                            | FSEL = 1                                        | 1.2  | 1.5   | 1.8  | μs               |

| t <sub>VW</sub>     | VERTICAL Width                              | FSEL = 0/1, standard NTSC                       | 196  | 198   | 200  | μs               |

| t <sub>VDD</sub>    | VERTICAL Default Delay                      | FSEL = 0                                        | 26.5 | 31.2  | 35.9 | μs               |

| t <sub>VDDF</sub>   | VERTICAL Default Delay                      | FSEL = 1                                        |      | 31.5  |      | μs               |

| f <sub>H</sub>      | Horiz Scan Rate                             |                                                 | 15   |       | 130  | kHz              |

| PARAMETER          | DESCRIPTION                         | CONDITIONS                                 | MIN  | TYP  | MAX | UNIT |

|--------------------|-------------------------------------|--------------------------------------------|------|------|-----|------|

| V <sub>LOSE</sub>  | Analog LOS Enable Threshold         | Minimum sync amplitude to enable outputs   |      | 120  |     | mV   |

| V <sub>LOSD</sub>  | Analog LOS Disable Threshold        | Maximum sync amplitude to disable outputs  |      | 80   |     | mV   |

| t <sub>JIT</sub>   | Output Jitter                       | All sync separator outputs                 |      | 5    |     | ns   |

| A <sub>SA</sub>    | SYNC AMP Gain                       |                                            | 1.7  | 2.0  | 2.3 |      |

| R <sub>SA</sub>    | SYNC AMP Output Impedance           |                                            |      | 200  |     | Ω    |

| V <sub>RFREQ</sub> | R <sub>FREQ</sub> Reference Voltage | $R_{FREQ}$ = 13k $\Omega$ to 130k $\Omega$ | 1.15 | 1.28 | 1.4 | V    |

**Electrical Specifications**  $V_S = V_{SD} = 5V$ , GND = 0V,  $T_A = 25^{\circ}C$ , Input Video =  $1V_{P-P}$ ,  $R_{FREQ} = 130k\Omega$  (Continued)

NOTES:

1.  $\mathsf{R}_L$  is Total Load Resistance due to Feedback Resistor and Load Resistor.

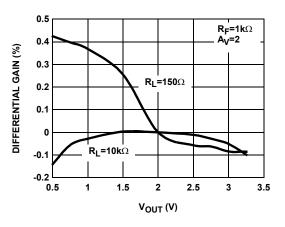

2. AC signal amplitude = 286mV<sub>PP</sub>, F = 3.58MHz, REF IN is swept from 0.8V to 3.4V, R<sub>L</sub> is DC coupled.

# **Typical Performance Curves**

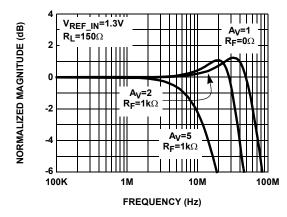

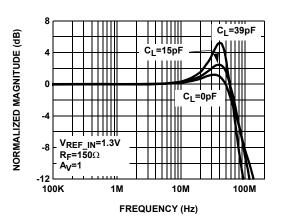

FIGURE 1. NON-INVERTING FREQUENCY RESPONSE (GAIN)

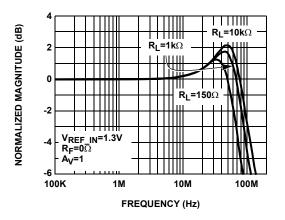

FIGURE 3. FREQUENCY RESPONSE FOR VARIOUS RL

4

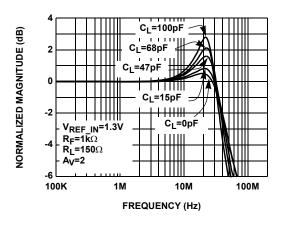

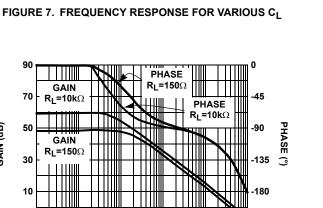

FIGURE 4. FREQUENCY RESPONSE FOR VARIOUS CL

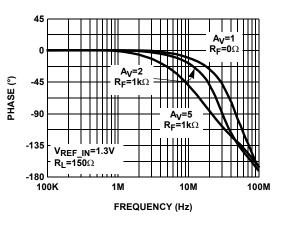

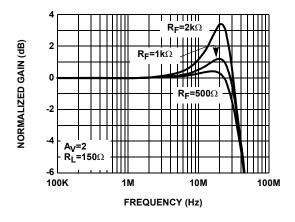

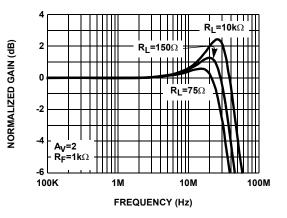

FIGURE 5. FREQUENCY RESPONSE FOR VARIOUS RF

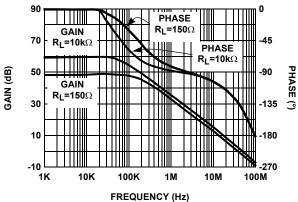

FIGURE 9. OPEN LOOP GAIN AND PHASE vs FREQUENCY

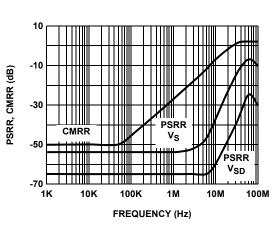

FIGURE 10. PSRR AND CMRR vs FREQUENCY - VIDEO AMP

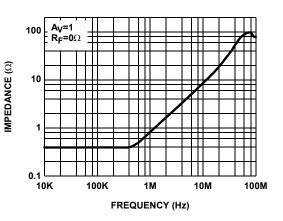

FIGURE 8. CLOSED LOOP OUTPUT IMPEDANCE

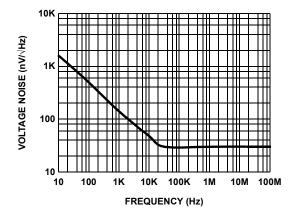

FIGURE 11. VOLTAGE NOISE vs FREQUENCY - VIDEO AMP

FIGURE 13. DIFFERENTIAL PHASE FOR RL TIED TO 0V

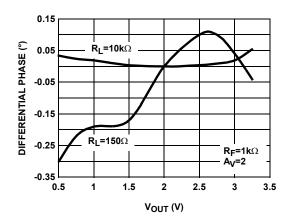

FIGURE 15. DIFFERENTIAL PHASE FOR RL TIED TO 0V

FIGURE 12. DIFFERENTIAL GAIN FOR RL TIED TO 0V

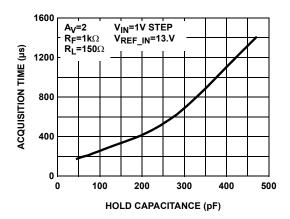

FIGURE 16. ACQUISITION TIME vs HOLD CAPACITANCE

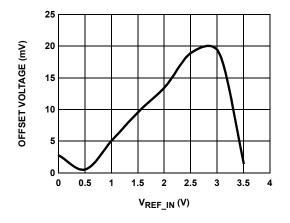

FIGURE 17. DC OFFSET VOLTAGE AT VOUT vs VREF\_IN

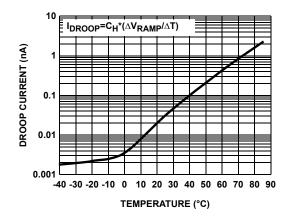

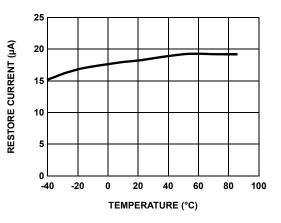

FIGURE 19. DROOP CURRENT vs TEMPERATURE

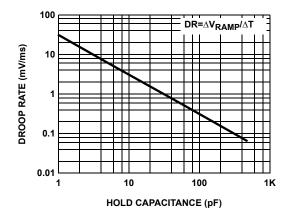

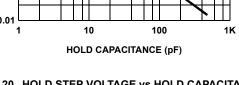

FIGURE 21. DROOP RATE vs HOLD CAPACITANCE

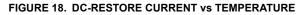

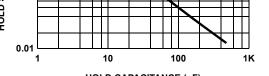

FIGURE 20. HOLD STEP VOLTAGE vs HOLD CAPACITANCE

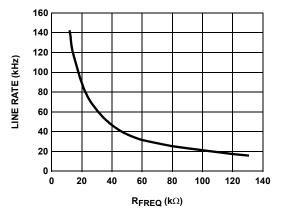

FIGURE 22. LINE RATE vs RFREQ

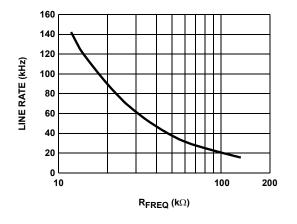

FIGURE 23. LINE RATE vs RFREQ

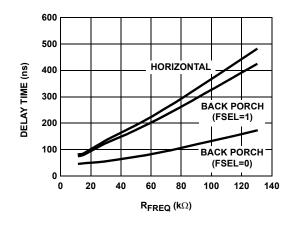

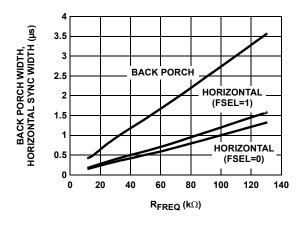

FIGURE 25. DELAY TIME vs RFREQ

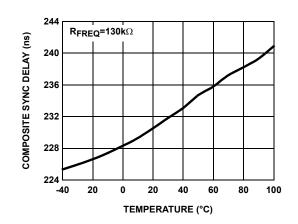

FIGURE 27. COMPOSITE DELAY vs TEMPERATURE -FSEL = 1

FIGURE 24. BACK PORCH AND HORIZONTAL SYNC WIDTH vs  $\mathsf{R}_{FREQ}$

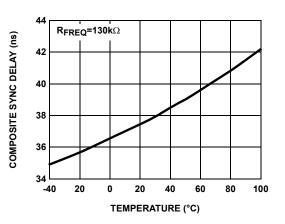

FIGURE 26. COMPOSITE DELAY vs TEMPERATURE -FSEL = 0

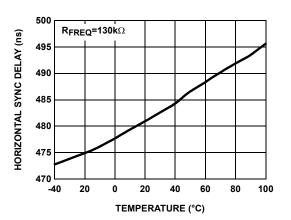

FIGURE 28. HORIZONTAL DELAY vs TEMPERATURE

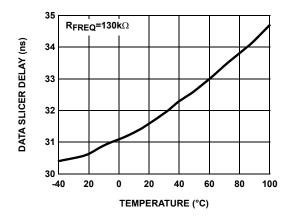

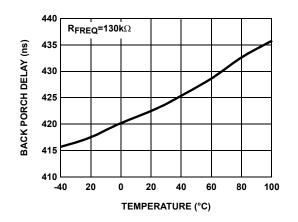

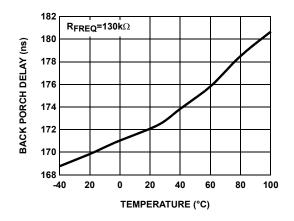

FIGURE 31. BACK PORCH DELAY vs TEMPERATURE -FSEL = 1

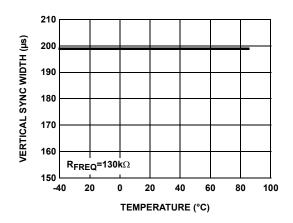

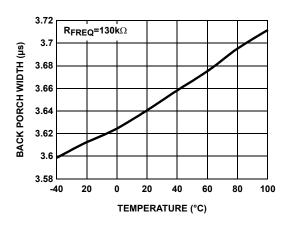

FIGURE 33. VERTICAL SYNC WIDTH vs TEMPERATURE

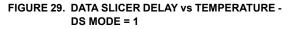

FIGURE 30. BACK PORCH DELAY vs TEMPERATURE -FSEL = 0

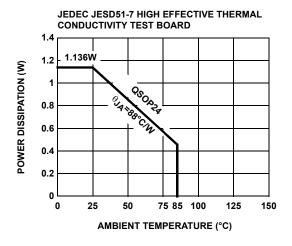

JEDEC JESD51-3 LOW EFFECTIVE THERMAL CONDUCTIVITY TEST BOARD 1.4 1.2 POWER DISSIPATION (W) 1 870mW 950p34 0.8 0JA=115°CM 0.6 0.4 0.2 0 25 0 50 75 85 100 125 150 AMBIENT TEMPERATURE (°C)

FIGURE 35. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

# **Timing Diagrams**

| FIELDS ONE AND THREE<br>(ODD) COMPOSITE SIGNAL |   |     |              |

|------------------------------------------------|---|-----|--------------|

| COMPOSITE SYNC OUTPUT                          |   |     |              |

| BURST/BACK PORCH OUTPUT                        |   |     | ᠾ᠆ᠾᢟᠾ᠆ᠾ᠆ᡁ᠆ᡁ᠆ |

| HORIZONTAL SYNC OUTPUT                         |   |     | ᠾᡙᢝᠾ᠊ᡙ᠆ᡁ᠆    |

| VERTICAL SYNC OUTPUT                           |   |     |              |

| ODD/EVEN OUTPUT                                |   |     |              |

| FIELDS TWO AND FOUR (EVEN)<br>COMPOSITE SIGNAL |   |     |              |

| COMPOSITE SYNC OUTPUT                          |   |     |              |

| BURST/BACK PORCH OUTPUT                        |   |     |              |

| HORIZONTAL SYNC OUTPUT                         |   |     |              |

| VERTICAL SYNC OUTPUT                           |   |     |              |

| ODD/EVEN OUTPUT                                |   |     |              |

|                                                | I | I I | i i i        |

# **Timing Diagrams**

# Standard (NTSC Input) H. Sync Detail

# **Pin Descriptions**

| PIN<br>NUMBER | PIN NAME  | PIN TYPE | PIN DESCRIPTION                                                                                                                 | EQUIVALENT CIRCUIT                                                              |

|---------------|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| 1             | VFB       | Input    | Connection for gain and feedback resistors, $R_{F}$ and $R_{G}$                                                                 | VS<br>VS<br>VS<br>VS<br>VS<br>VS<br>VS<br>VS<br>VS<br>VS<br>VS<br>VS<br>VS<br>V |

| 2             | VIDEO IN  | Input    | Input to DC-restore amplifier; input coupling capacitor connects from here to video source                                      |                                                                                 |

| 3             | DS MODE   | Input    | Sets the mode of the DS comparator; logic low selects<br>a standard logic output; logic high selects an open<br>drain/collector | VS<br>VS<br>CIRCUIT 3                                                           |

| 4             | DS ENABLE | Input    | Enables the output of the comparator; a logic high<br>enables the comparator; a logic low three-states it                       | Vs<br>Vs<br>GND<br>CIRCUIT 4                                                    |

| 5             | GND       | Input    | Analog ground                                                                                                                   |                                                                                 |

| 6             | GNDD      | Input    | Digital ground                                                                                                                  |                                                                                 |

| 7             | RFREQ     | Input    | Connection for bias resistor that sets the overall timing                                                                       |                                                                                 |

# **Pin Descriptions**

|    | PIN NAME   | PIN TYPE | PIN DESCRIPTION                                                                                                           | EQUIVALENT CIRCUIT                                       |

|----|------------|----------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 8  | FSEL       | Input    | Enable/bypass internal brick wall filter; a logic high is<br>used to enable the filter; a logic low to disable it         |                                                          |

| 9  | SYNC IN    | Input    | Input to the sync separator; connects to the video<br>source via a coupling capacitor or to a color burst input<br>filter | CIRCUIT 7                                                |

| 10 | LOS        | Output   | Loss of signal output; goes high if no input video signal<br>is detected                                                  |                                                          |

| 11 | COMPOSITE  | Output   | Composite sync output                                                                                                     | Reference circuit 8                                      |

| 12 | HORIZONTAL | Output   | Horizontal sync output                                                                                                    | Reference circuit 8                                      |

| 13 | VERTICAL   | Output   | Vertical sync output                                                                                                      | Reference circuit 8                                      |

| 14 | ODD/EVEN   | Output   | Odd/even field indicator output                                                                                           | Reference circuit 8                                      |

| 15 | BACK PORCH | Output   | Back porch output                                                                                                         | Reference circuit 8                                      |

| 16 | SLICE MODE | Input    | Low = 50% slicing level; high = 70mV fixed slicing level                                                                  | Reference circuit 8                                      |

| 17 | SYNC AMP   | Output   | Amplitude of sync tip; can be used to control AGC circuit                                                                 | VS<br>VS<br>VS<br>VS<br>VS<br>VS<br>VS<br>VS<br>VS<br>VS |

| 18 | VSD<br>VS  | Input    | Digital power supply; nominally +5V<br>Analog power supply; nominally +5V                                                 | V <sub>SD</sub> CIRCUIT 10<br>Reference circuit 10       |

# **Pin Descriptions**

| PIN<br>NUMBER | PIN NAME  | PIN TYPE | PIN DESCRIPTION                                                                                                                         | EQUIVALENT CIRCUIT                         |

|---------------|-----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 20            | REF OUT   | Output   | Voltage reference for use as blanking level in low cost system                                                                          | VS<br>···································· |

| 21            | REF IN    | Input    | DC voltage on this pin sets the DC-restore voltage and output blanking level                                                            | VS<br>GND<br>CIRCUIT 12                    |

| 22            | DS REF    | Input    | Sets the slicing level or reference level for the comparator                                                                            |                                            |

| 23            | DS OUT    | Output   | Output of the data slicing comparator; the output is<br>either open drain or standard symmetrical logic<br>depending on the DS MODE pin | Vs<br>Vs<br>I<br>GND<br>CIRCUIT 14         |

| 24            | VIDEO OUT | Output   | Output of DC-restore amplifier                                                                                                          |                                            |

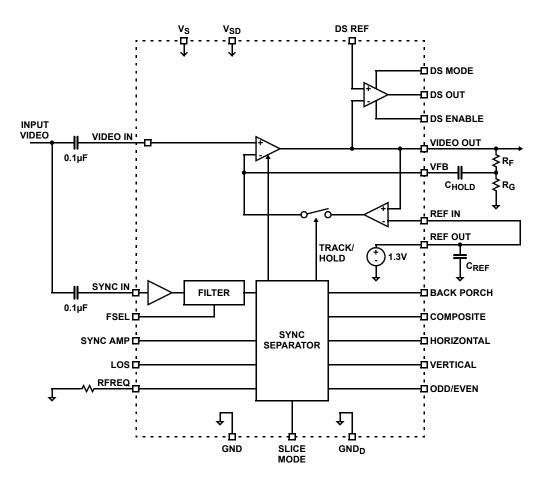

# Block Diagram

# Applications Information

# **Product Description**

The EL4501 is a video front-end sub-system comprised of a video amplifier with DC-restore, an adjustable threshold data slicer, and an advanced sync separator. The prime function of the system is to DC-stabilize and buffer AC-coupled analog video signals and to extract timing reference signals embedded in the video signal. An adjustable threshold data slicer incorporated into the EL4501 may be used to extract data embedded within the active video or VBI regions of a video signal.

# Theory of Operation

# **DC-RESTORE LOOP**

When video signals are distributed, it is common to employ capacitive coupling to prevent DC current flow due to differences in local grounds or signal reference levels. However, the coupling capacitor causes the DC level of the signal post capacitor to be dependent on the video (luminance) content of the waveform. A DC-restore loop is used to correct this behavior by moving a portion of the video waveform to a DC reference level in response to a control signal. When the loop is operating, DC drift

accumulates over a single line only, before it is corrected. The peak value of drift is limited by the rate of the control signal (typically video line rate) and the AC coupling time constant.

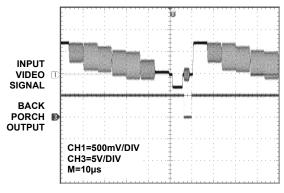

The restore loop is comprised of a 100MHz forward video amplifier, combined with a nulling amplifier and sample and hold circuit. For maximum flexibility the hold capacitor is placed off-chip, allowing the loop response rate to be tailored for specific applications and minimizing hold-step problems. The loop provides a restore current peak of ±20µA at room temperature. Figure 36 shows the amplifier and S/H connection. During normal operation the internally generated DC-restore control signal is timed to the back porch of the video waveform. Figure 37 shows an NTSC video signal, along with the EL4501 BACK PORCH output. In operation, BACK PORCH activates the S/H switch, completing the nulling feedback loop and driving the video amplifier output towards the reference voltage. At the end of BACK PORCH, the external capacitor holds the correction voltage for the remainder of the video line. In the absence of a valid input signal, the chip generates a repetitive, arbitrary restore control signal at the line rate set by the external resistor REREQ. Although uncorrelated to the input, the pulse

prevents the amplifier output drifting significantly from the DC-restore reference level. This improves start-up behavior and speeds recovery after a signal drop-out. For ease of use, the EL4501 provides a buffered 1.3V DC level normally connected directly to the restore loop reference input (REF IN). Alternatively, an external voltage between 0V and 3.5V, connected to REF IN, can be used to set the restored level.

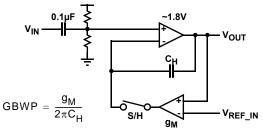

FIGURE 36. DC-RESTORE AMPLIFIER AND S/H CONFIGURATION

FIGURE 37. NTSC VIDEO SIGNAL WITH BACK PORCH OUTPUT

#### Auto-Zero Loop Bandwidth

The gain bandwidth product (GBWP) of the auto-zero loop is determined by the size of the hold capacitor and the transconductance (g<sub>M</sub>1) of the sample and hold amplifier. GBWP = g<sub>M</sub>1 / ( $2\pi * C_H$ ), gM1 is about 1/(29k $\Omega$ ), for C<sub>H</sub> = 270pF, GBWP is 20kHz. For C<sub>H</sub> = 100pF, GBWP is about 55kHz.

#### **Charge Injection and Hold Step Error**

Charge injection refers to the charge transferred to the hold capacitor when switching to the hold mode. The charge should ideally be 0, but due to stray capacitive coupling and other effects, it is typically 6fC. This charge changes the hold capacitor voltage by  $\Delta V = \Delta Q / C_H$  and will shift the output voltage of the video amplifier by  $\Delta V$ . However, this shift is small and can be negligible for the EL4501 (see the Hold Step Voltage Error vs Hold Capacitance curve). Assuming  $C_H = 100 \text{pF}, \Delta V$  is about 60  $\mu$ V. There will be 60  $\mu$ V change at the video amplifier output.

#### Droop Rate

When the S/H amplifier is in the hold mode, there is a small current that leaks from the switch to the hold capacitor. This

quantity is called the droop current. This droop current produces a ramp in the hold capacitor voltage, which in turn produces a similar voltage at the video amplifier output. The droop rate at the video amplifier output can be found using the following equation:

$$DroopRate = \frac{\Delta V_{RAMP}}{\Delta t}$$

Assuming  $C_H = 100$  pF, from the Droop Rate vs Hold Capacitance curve, the droop rate is about 0.31 mV/ms at the video amplifier output at room temperature. In NTSC applications, there is about 60 µs between auto-zero periods. Thus, there is (0.31 mV/ms) \* 60 µs = 18.6 µV. It is much less than 0.5IRE (3.5 mV). This drift is negligible.

#### **Choice of Hold Capacitor**

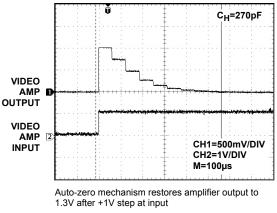

The EL4501 allows the user to choose the hold capacitor as low as 1pF and it is still stable. A smaller hold capacitor has a faster acquisition time and faster auto-zero loop response, but would increase the droop and hold step error. Also, if the acquisition time is too fast, it would probably give an image with clamp streaking and low frequency noise with noisy signals. Increasing the hold capacitor would increase the acquisition time, lower the auto-zero loop response, lower the droop and hold step error. See the performance curves for the trade-off. Normally, in video (NTSC and PAL) applications, a smooth acquisition might takes about 10 to 20 scan lines. For a hold capacitor equal to 270pF, the acquisition time is about 10 lines. In the worse case, ambient temperature is 85°C, the droop current is 2.2nA which causes the output voltage ramp to about 0.49mV for 60µs. This drift is negligible in most applications. Figure 38 shows the input and output waveforms of the video amplifier while the S/H is in sample mode. Applying a 1V step to the video amplifier input, the output of the video amplifier jumps to 2.3V. Then, the auto-zero system tries to drive the video output to the reference voltage, which is 1.3V. The acquisition time takes about 10 NTSC scan lines.

# DATA SLICER

The data slicer is a fast comparator with the output of the video amplifier connected to its inverting input and the DS REF connected to its non-inverting input. The DS OUT is logical inverse of the video output sliced at the DS REF voltage. The propagation delay from the video amplifier output to the DS OUT is about 18ns. There is about 10mV hysteresis added internally in the comparator to prevent the oscillation at the DS OUT when the voltages at the two inputs are very close or equal. An adjustable DS REF voltage may be used to extract data embedded within the active video or video blanking interval regions of a video signal. Logic low at the DS ENABLE pin enables the comparator and logic low lets the DS OUT be three-state. The DS MODE pin sets the mode of the DS comparator. Logic low at the DS MODE pin selects a standard logic output and a logic high selects an open drain/collector output.

# VIDEO AMPLIFIER

The EL4501 DC-restore block incorporates a wide bandwidth, single supply, low power, rail-to-rail output, voltage feedback operational amplifier. The amplifier is internally compensated for closed loop feedback gains of +1 or greater. Larger gains are acceptable but bandwidth will be reduced according to the familiar Gain-Bandwidth product.

Connected in a voltage follower mode and driving a high impedance load, the amplifier has a -3dB bandwidth of 100MHz. Driving a  $150\Omega$  load, the -3dB bandwidth reduces to 60MHz while maintaining a 200V/µs slew rate.

# CHOICE OF FEEDBACK RESISTOR, RF

The video amplifier is optimized for applications that require a gain of +1. Hence, no feedback resistor is required. However, for gains greater than +1, the feedback resistor forms a pole with the hold capacitance. As this pole becomes larger, phase margin is reduced. This causes ringing in the time domain and peaking in the frequency domain. Therefore, RF has some maximum value that should not be exceeded for optimum performance. If a large value of R<sub>F</sub> must be used, a small capacitor in the few picofarad range in parallel with R<sub>F</sub> can help to reduce ringing and peaking at the expense of reducing the bandwidth. As far as the output stage of the amplifier is concerned, R<sub>F</sub> + R<sub>G</sub> appear in parallel with R<sub>L</sub> for gains other than +1. As this combination gets smaller, the bandwidth falls off. Consequently R<sub>F</sub> also has a minimum value that should not be exceeded for optimum performance.

- For  $A_V$  = +1,  $R_F$  = 0 $\Omega$  is optimum

- For A<sub>V</sub> = +2, R<sub>F</sub> between 300 $\Omega$  and 1k $\Omega$  is optimum

# VIDEO PERFORMANCE

For good video signal integrity, an amplifier is required to maintain the same output impedance and frequency response as DC levels are changed at the output. This can

be difficult when driving a standard video load of  $150\Omega$ because of the change in output current with DC level. A look at the Differential Gain and Differential Phase curves will help to obtain optimal performance. Curves are provided for A<sub>V</sub> = +1 and +2, and R<sub>L</sub> =  $150\Omega$  and  $10k\Omega$ . As with all video amplifiers, there is a common mode sweet spot for optimum differential gain/differential phase. For example, with  $A_V = +1$  and  $R_I = 150\Omega$  and the video level kept between 1V and 3V, the amplifier will provide dG/dP performance of 0.17%/0.07°. This condition is representative of using the amplifier as a buffer driving a DC coupled, double terminated,  $75\Omega$  coaxial cable. Driving high impedance loads, such as signals on computer video cards gives much better dG/dP performance. For  $A_V = 1$ ,  $R_{I} = 10k\Omega$ , and the video level kept between 1V and 3V, the dG/dP are 0.03%/0.02°.

# SHORT-CIRCUIT CURRENT LIMIT

The EL4501 video amplifier has no internal short circuit protection circuitry. Short circuit current of 90mA sourcing and 65mA sinking typically will flow if the output is shorted midway between the rails. If the output is shorted indefinitely, the power dissipated could easily increase the die temperature such that the part will be destroyed. Maximum reliability is maintained if the output current never exceeds ±50mA. This limit is set by internal metal interconnect limitations. Obviously, short circuit conditions must not be allowed to persist or internal metal connections will be damaged or destroyed.

# DRIVING CABLES AND CAPACITIVE LOADS

The EL4501 video amplifier can drive 39pF loads in parallel with 150 $\Omega$  with 5dB of peaking. For less peaking in theses applications a small series resistor of between 5 $\Omega$  and 50 $\Omega$  can be placed in series with the output. However, this will obviously reduce the gain slightly. If your gain is greater than 1, the gain resistor R<sub>G</sub> can be adjusted to make up for any lost gain caused by the additional output resistor. Peaking may also be reducing by adding a "snubber" circuit at the output. A snubber is a resistor in series with a capacitor, 150 $\Omega$  and 100pF being typical values. The advantage of a snubber is that it does not draw DC load current.

When used as a cable driver, double termination is always recommended for reflection-free performance. For those applications, the back-termination series resistor decouples the video amplifier from the cable and enables extensive capacitive drive. However, other applications may have high capacitive loads without a back-termination resistor. Again, a small series resistor at the output can reduce peaking.

# VIDEO SYNC SEPARATOR

The EL4501 includes an advanced sync separator, which is used to generate the DC-restore control signal and seven major sync outputs. The advanced sync separator operates at a 5V DC (pin VSD) single-supply voltage. The input signal source is composite video with levels of  $0.5V_{P-P}$  to  $2.0V_{P-P}$ .

Low jitter, temperature-stable timing signals are generated using a master time-base, embedded within the system. Line rate is adjustable from 10kHz to 135kHz using a single external resistor ( $R_{FREQ}$ ). An integrated, pin-selectable digital filter tracks line rate and rejects high frequency noise and video artifacts, such as color burst. In addition to the digital filter, a window-based, time qualification scheme is employed to improve recovered signal quality. During loss of signal, all outputs are blanked to prevent output chatter caused by input noise.

#### **Composite Sync Output**

The composite sync output is a reproduction of the signal waveform below the composite video black level, with the video completely removed. The composite video signal is AC-coupled to SYNC IN (pin 9). The video signal passes through a comparator whose threshold is controlled by the SLICE MODE pin. The output of the comparator is buffered to the COMPOSITE output (pin 11) as a CMOS logic signal.

### Horizontal Sync Output

The horizontal circuit triggers on the falling edge of the sync tip of the input composite video signal and produces a horizontal output with pulse widths about 12 times the internal oscillator clock. For NTSC video input, the pulse width of the horizontal sync is 1.5µs, with the digital filter selected. The half line pulses present in the input signal during vertical blanking are removed with an internal 2H-eliminator circuit.

# Vertical Sync Output

A low-going vertical sync pulse is generated during the start of the vertical cycle of the incoming composite video signal. The vertical output pulse is started on the first serration pulse in the vertical interval and is ended on the second rising edge during the vertical serration phase. In the absence of vertical serration pulses, a vertical sync pulse will be forced out after the vertical sync default delay time, approximately 31µs after the last falling edge of the vertical pre-equalizing pulse for R<sub>FREQ</sub> = 130kΩ.

#### **Back Porch Output**

In a composite video signal, the chroma burst is located on the back porch of the horizontal blanking period and is also the black level reference for the subsequent video scan line. The back porch is triggered from the rising edge of the sync tip. The pulse width of the back porch is about 29 times the internal oscillator clock cycle. For the NTSC video input, the pulse width of the back porch is about 3.5µs. In EL4501, the back porch pulse controls the sample and hold switch of the DC-restored loop.

# Odd and Even Output

For a composite video signal that is interlaced, there is an odd field that includes all the odd lines, and an even field that consists of the even lines. The odd and even circuit tracks the relationship of the horizontal pulses to the leading edge of the vertical output and will switch on every field at the start of vertical sync pulse interval. ODD/EVEN, pin 14 is high during the odd field and low during the even field.

### Sync Amplitude Output

The output voltage at the SYNC AMP output (pin 17) is about 2 times the sync tip voltage. This signal can be used for AGC applications. When there is no sync signal at the input, the SYNC AMP output is 0V.

### Loss of Sync Output

Loss of video signal can be detected by monitoring the LOS output at pin 10. LOS goes low indicating the EL4501 has locked to the right line rate. LOS goes high indicating the EL4501 is out of lock. When there is loss of sync, all the sync outputs go high, except ODD/EVEN.

#### **Digital Filter Operation**

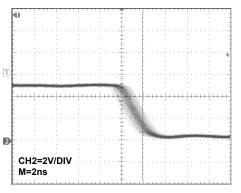

The EL4501 contains a user-selectable digital filter which tracks the line rate and rejects high frequency noise and video artifacts, such as color burst. Basically, the digital filter delays all signals and filters out the pulses which are shorter than the filters delay time. The digital filter greatly reduces the jitters in the outputs. With the digital filter on, the jitter at the composite sync output is only 2ns. Figure 39 shows the jitter at the output when the digital filter is selected. However, the output waveforms will be delayed from 150ns to 300ns due to this filter. Refer to the performance curves for details. Applying logic high to the FSEL pin, the digital filter is enabled. Applying a logic low to the FSEL pin, the digital filter is disabled.

FIGURE 39. JITTER AT THE OUTPUTS WITH FSEL=1

# R<sub>FREQ</sub>

An external  $R_{FREQ}$  resistor, connected from pin 7 to ground, produces a reference current that is used internally as the timing reference for all the sync output delay time and output pulse widths. Decreasing the value of  $R_{FREQ}$  increases the reference current and frequency of the internal oscillator, which in turn decreases the reference time and pulse width. A higher frequency video input requires a lower  $R_{FREQ}$ value. The Line Rates vs  $R_{FREQ}$  performance curve shows the variation of line rate with  $R_{FREQ}$ .

#### Slice Mode and Operation with VCRs

Normally the signal source for the EL4501 is assumed to be clean and relatively noise free. If that is the case, the SLICE MODE pin (pin 16) should be connected to ground, which sets the slice level to 50% of the sync tip. Some signal sources may have excessive video peaking, causing high frequency video and chroma components to extend below the black level reference, such as VCR signals which generate lots of head switching noise. In this case, the SLICE MODE pin should be connected to logic high which sets the slice level to a fixed 100mV above the sync tip. Also, a single pole chroma filter is required at the composite video input to increase the S/N ratio of the incoming noisy video signal. When the source impedance is low, typically  $75\Omega$ , a  $620\Omega$  resistor in series with the source and 470pF capacitor to ground will form a low pass filter with a roll-off frequency of about 550kHz. This bandwidth sufficiently attenuates the 3.58MHz (NTSC) or 4.43MHz (PAL) color burst signal and high frequency spikes, yet passes the sync pulse portion without appreciable attenuation. The chroma filter will increase the propagation delay from the composite sync input to the outputs. Applying a chroma filter, setting the SLICE MODE pin and FSEL pin to high greatly improve the noise immunity performance in VCR applications.

#### **Output Drive Capability**

The outputs of the sync separator are not designed to drive heavy loads. For a 5V VDS, if the output is driving  $5k\Omega$  load to ground, the output high voltage is about 4.9V. If the output is driving  $500\Omega$  load, the output high voltage is down to 4.2V.

# General

# **Power Dissipation**

With the high output drive capability of the EL4501 video amplifier, it is possible to exceed the 125°C Absolute Maximum junction temperature under certain load current conditions. It is important to calculate the maximum junction temperature for a given application to determine if load conditions or package type need to be modified for the amplifier to remain in its safe operating region.

The maximum power dissipation allowed in a package is determined according to:

$$\mathsf{P}_{\mathsf{DMAX}} = \frac{\mathsf{T}_{\mathsf{JMAX}} - \mathsf{T}_{\mathsf{AMAX}}}{\Theta_{\mathsf{JA}}}$$

#### where:

- T<sub>JMAX</sub> = Maximum junction temperature (125°C)

- T<sub>AMAX</sub> = Maximum ambient temperature (85°C)

- θ<sub>JA</sub> = Thermal resistance of the package

- P<sub>DMAX</sub> = Maximum power dissipation in the package

The maximum power dissipation actually produced by an IC is the product of total quiescent supply current and power supply voltage, plus the power in the IC due to the load. Assume no load at the sync separator outputs:

$$P_{DMAX} = V_{S} \times I_{SMAX} + V_{SD} \times I_{SDMAX} + \left[ (V_{S} - V_{OUT}) \times \frac{V_{OUT}}{R_{L}} \right]$$

where:

- V<sub>S</sub> = Supply voltage

- V<sub>SD</sub> = Digital supply

- I<sub>SMAX</sub> = Maximum supply current

- I<sub>SDMAX</sub> = Maximum digital supply current

- V<sub>OUT</sub> = Maximum output voltage

- R<sub>L</sub> = Load resistance tied to ground

#### **Board Layout**

As with any high frequency device, good printed circuit board layout is necessary for optimum performance. Ground plane construction is highly recommended. Lead lengths should be as short as possible. The power supply pin must be well bypassed to reduce the risk of oscillation. In normal operation, where the GND pin is connected to the ground plane, a single 4.7µF tantalum capacitor in parallel with a 0.1µF ceramic capacitor from VS to GND will suffice. To reduce cross talk between the analog signal path and the embedded sync separator, a separate digital supply pin, VSD is included on the EL4501. This pin should be bypassed in a similar manner to V<sub>S</sub>. For additional isolation a ferrite bead may be added in line with the supply connections to both pins. For good AC performance, parasitic capacitance should be kept to a minimum. Use of wire wound resistors should be avoided because of their additional series inductance.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's guality certifications can be viewed at www.intersil.com/design/guality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com